#### GM8136S/GM8135S

## H.264 IP-CAM SOC

**Data Sheet**

Rev.: 0.2

Issue Date: October 2014

#### **REVISION HISTORY**

#### GM8136S/GM8135S Data Sheet

| Date       | Rev. | From | То                                                                                            |

|------------|------|------|-----------------------------------------------------------------------------------------------|

| Sept. 2014 | 0.1  | -    | Original                                                                                      |

| Oct. 2014  | 0.2  | -    | <ul> <li>Updated Figure 2-3 and Figure 2-4</li> </ul>                                         |

|            |      |      | <ul> <li>Updated Table 2-2, Table 4-17, Table 4-24, Table 4-34,<br/>and Table 4-36</li> </ul> |

Copyright © 2014 Grain Media, Inc.

All Rights Reserved.

Printed in Taiwan 2014

Grain Media and the Grain Media Logo are trademarks of Grain Media, Inc. in Taiwan and/or other countries. Other company, product and service names may be trademarks or service marks of others.

All information contained in this document is subject to change without notice. The products described in this document are NOT intended for use in implantation contained in this document is subject to change without notice. The products described in this document are NOT interlocation where malfunction may result in injury or death to persons. The information contained in this document does not affect or change Grain Media's product specification or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of Grain Media or third parties. All information contained in this document was obtained in specific environments, and is presented as an illustration. The results obtained in other operating environments may vary.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS. In no event will Grain Media be liable for damages arising directly or indirectly from any use of the information contained in this document.

Grain Media, Inc. 5F, No. 5, Li-Hsin Road III, Hsinchu Science Park, Hsinchu City, Taiwan 300, R.O.C.

Grain Media's home page can be found at: http://www.grain-media.com

## **TABLE OF CONTENTS**

| Chapter 1 | Introduction |                        |                                               | 1  |

|-----------|--------------|------------------------|-----------------------------------------------|----|

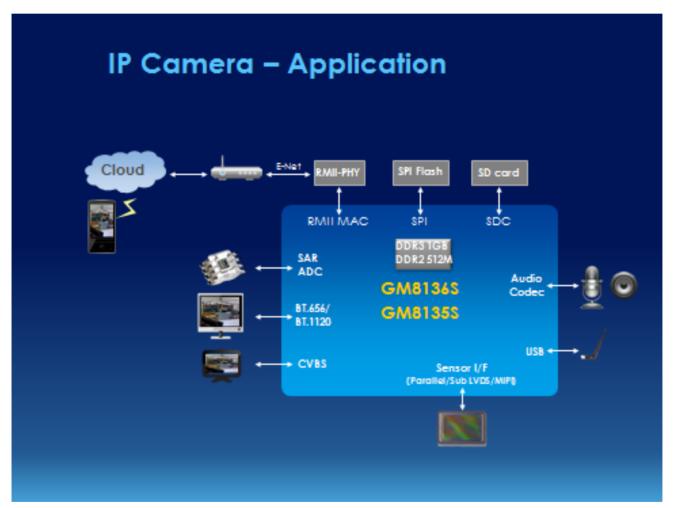

|           | 1.1          | Applica                | ation Scenarios                               | 2  |

|           | 1.2          | Feature                | es                                            | 3  |

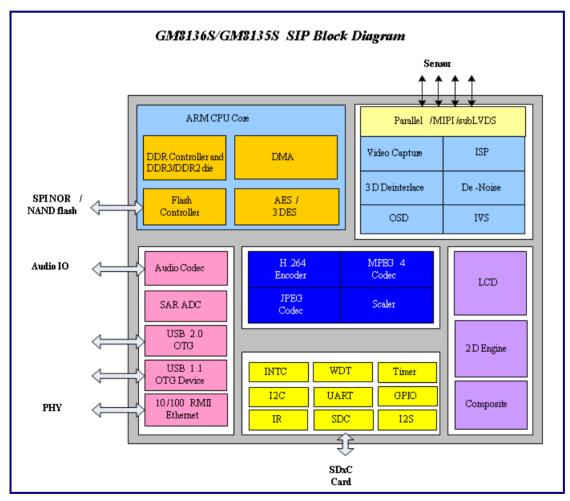

|           | 1.3          | Function               | onal Block Diagram                            | 6  |

|           |              | 1.3.1                  | DDR3/DDR2 SDRAM Controller (DDRC)             | 7  |

|           |              | 1.3.2                  | Serial Peripheral Interface Controller (SPIC) | 7  |

|           |              | 1.3.3                  | H.264 Encoder (H264E)                         | 7  |

|           |              | 1.3.4                  | MPEG4/JPEG Engine                             | 8  |

|           |              | 1.3.5                  | 3D De-interlace and De-noise Filter (3DI/DN)  | 9  |

|           |              | 1.3.6                  | 2D Graphic Accelerator Engine                 | 10 |

|           |              | 1.3.7                  | Image Signal Pocessor (ISP)                   | 10 |

|           |              | 1.3.8                  | Intelligent Video Surveillance Engine (IVS)   | 11 |

|           |              | 1.3.9                  | Video Scaler                                  | 11 |

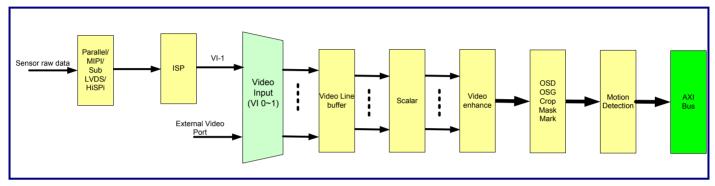

|           |              | 1.3.10                 | Video Capture                                 | 12 |

|           |              | 1.3.11                 | Display Controller                            | 13 |

|           |              | 1.3.12                 | I <sup>2</sup> S Controller                   | 13 |

|           |              | 1.3.13                 | Mega Ethernet Controller (RMII MAC)           | 14 |

|           |              | 1.3.14                 | Secure Digital Card Controller (SDC)          | 15 |

|           |              | 1.3.15                 | AES/DES/TDES Cipher Controller                | 16 |

|           |              | 1.3.16                 | Timer                                         | 16 |

|           |              | 1.3.17                 | WatchDog Timer (WDT)                          | 17 |

|           |              | 1.3.18                 | GPIO                                          | 17 |

|           |              | 1.3.19                 | I <sup>2</sup> C Bus                          | 18 |

|           |              | 1.3.20                 | UART Controller                               | 18 |

| Chapter 2 | Sign         | al Descri <sub>l</sub> | ption                                         | 19 |

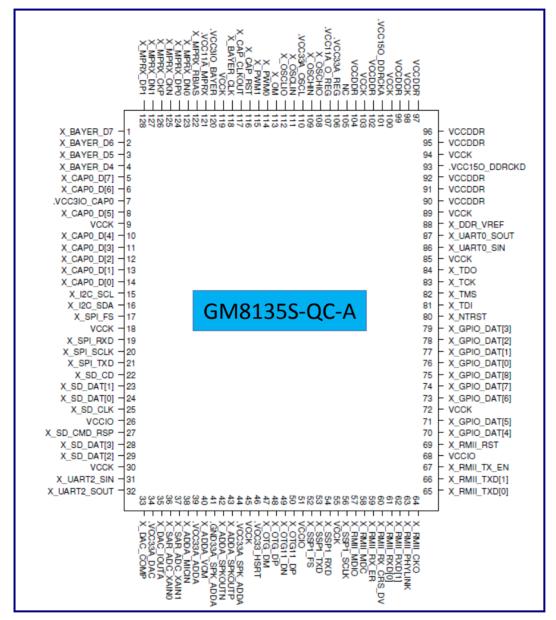

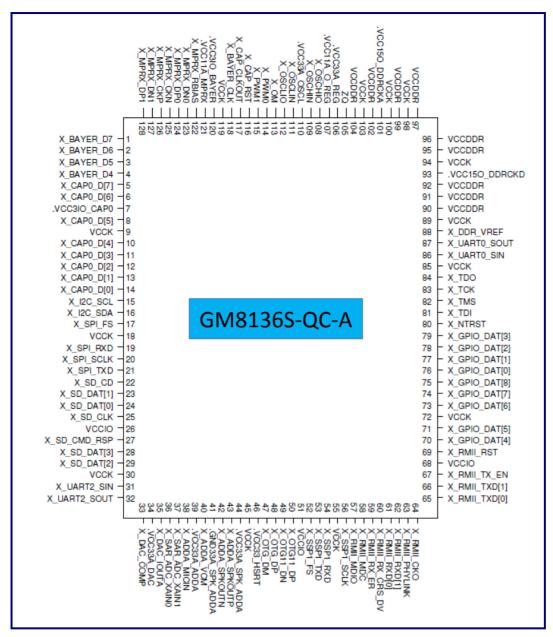

|           | 2.1          | Signal                 | Descriptions                                  | 20 |

|           | 2.2          | Pin Ass                | signments                                     | 38 |

| Chapter 3 | Mem          | nory Map               |                                               | 43 |

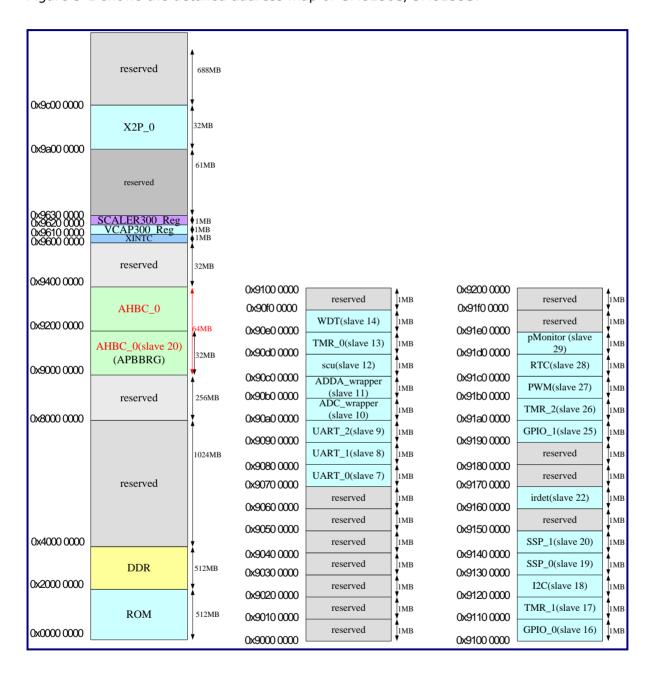

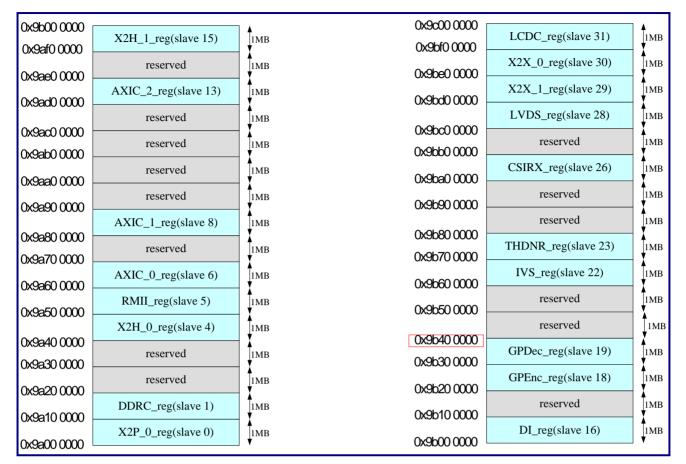

|           | 3.1          | Addres                 | ss Map                                        | 44 |

| Chapter 4 | System Control Unit |            | 47                              |     |

|-----------|---------------------|------------|---------------------------------|-----|

|           | 4.1                 | Syster     | m Controller                    | 48  |

|           |                     | 4.1.1      | General Description             | 48  |

|           |                     | 4.1.2      | Features                        | 48  |

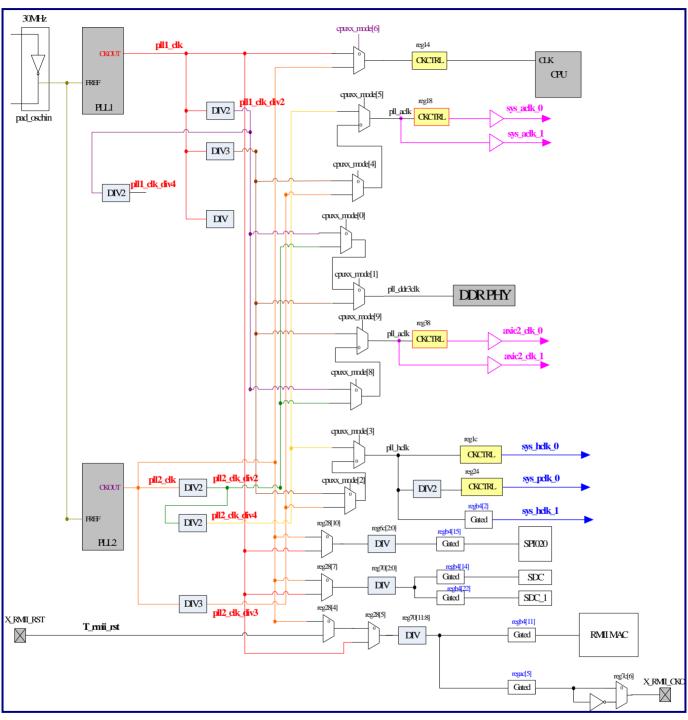

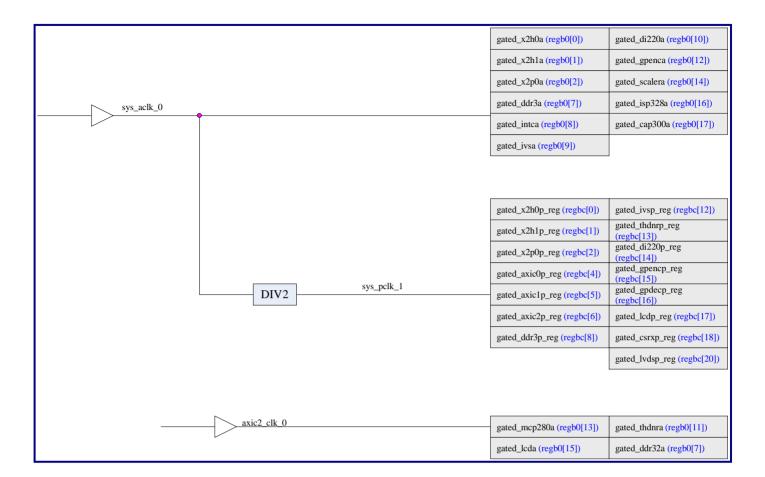

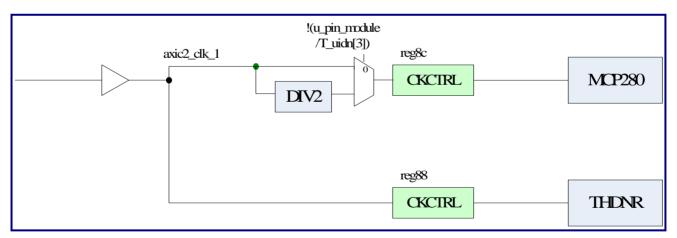

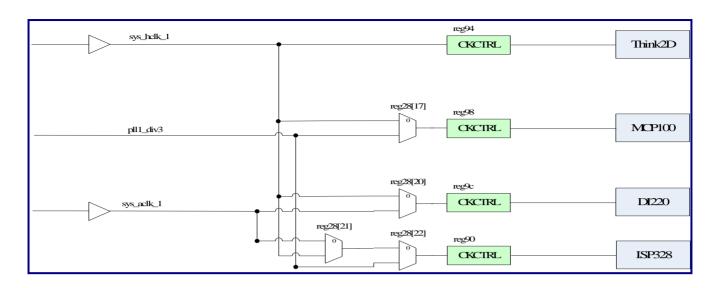

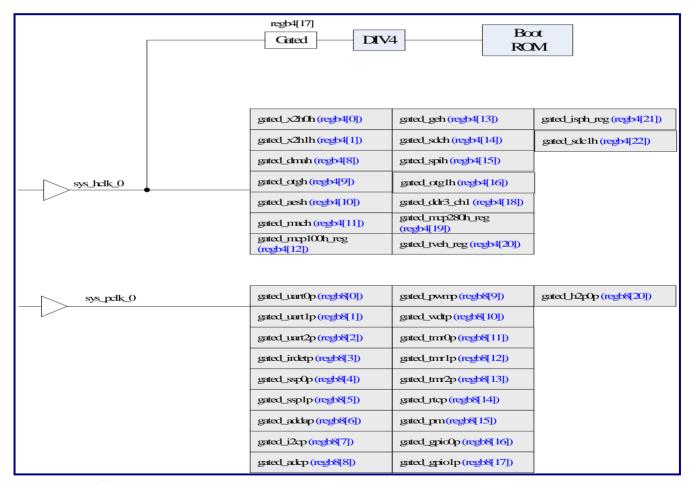

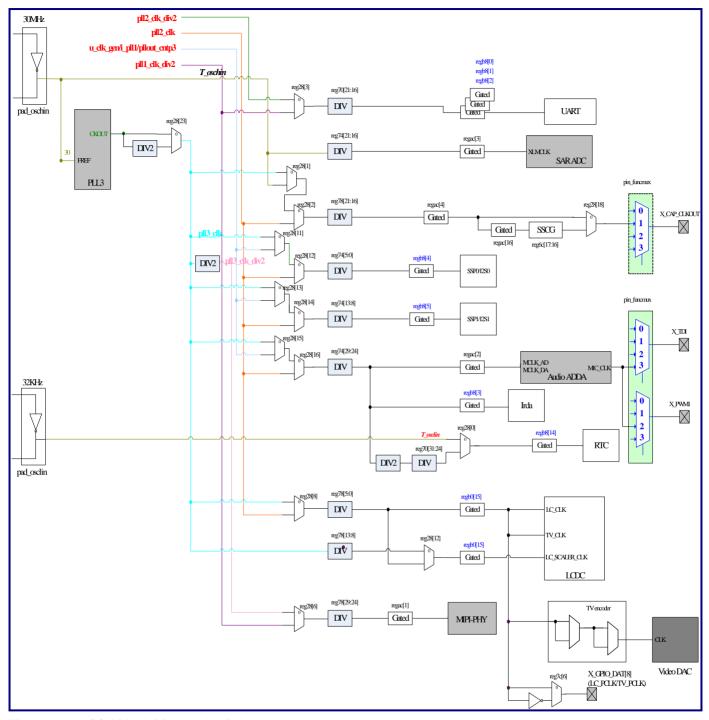

|           |                     | 4.1.3      | Clock Manager                   | 49  |

|           |                     | 4.1.4      | Programming Model               | 56  |

|           | 4.2                 | Interru    | upt Controller                  | 121 |

|           |                     | 4.2.1      | Features                        | 121 |

|           |                     | 4.2.2      | Interrupt Routing               | 122 |

|           |                     | 4.2.3      | Programming Model               | 125 |

|           |                     | 4.2.4      | Functional Description          | 141 |

|           |                     | 4.2.5      | Initialization                  | 143 |

|           | 4.3                 | Timer      |                                 | 144 |

|           |                     | 4.3.1      | General Description             | 144 |

|           |                     | 4.3.2      | Features                        | 144 |

|           |                     | 4.3.3      | Programming Model               | 145 |

|           | 4.4                 | Watch      | Dog Timer                       | 151 |

|           |                     | 4.4.1      | General Description             | 151 |

|           |                     | 4.4.2      | Features                        | 152 |

|           |                     | 4.4.3      | Programming Model               | 152 |

| Chapter 5 | Encryption          |            |                                 | 157 |

|           | 5.1                 | AES-D      | DES Cipher Coprocessor          | 158 |

|           |                     | 5.1.1      | General Description             | 158 |

|           |                     | 5.1.2      | Features                        | 159 |

|           |                     | 5.1.3      | Functional Description          | 159 |

|           |                     | 5.1.4      | Register Descriptions           | 160 |

|           |                     | 5.1.5      | Programming Sequence            | 169 |

| Chapter 6 | Mem                 | nory Inter | rface                           | 173 |

|           | 6.1                 | DDR3       | /DDR2 Memory Controller         | 174 |

|           |                     | 6.1.1      | General Description             | 174 |

|           |                     | 6.1.2      | Features                        | 174 |

|           |                     | 6.1.3      | Functional Description          | 175 |

|           |                     | 6.1.4      | Programming Model               | 177 |

|           |                     | 6.1.5      | Memory Address Table (MA Table) |     |

|           |                        | 6.1.6      | Initialization Sequence                | 234 |

|-----------|------------------------|------------|----------------------------------------|-----|

|           | 6.2                    | SPI N      | AND/NOR Flash Controller               | 239 |

|           |                        | 6.2.1      | General Description                    | 239 |

|           |                        | 6.2.2      | Features                               | 239 |

|           |                        | 6.2.3      | Memory Map/Register Definition         | 239 |

|           |                        | 6.2.4      | Functional Description                 | 247 |

|           |                        | 6.2.5      | Initialization                         | 253 |

| Chapter 7 | Vide                   | o Input II | nterface                               | 255 |

|           | 7.1                    | Video      | Input Interface                        | 256 |

|           | 7.2                    | Captu      | re (Including MD)                      | 256 |

|           |                        | 7.2.1      | General Description                    | 256 |

|           |                        | 7.2.2      | Features                               | 257 |

|           |                        | 7.2.3      | Memory Map/Register Definition         | 260 |

|           | 7.3                    | CSIRX      | X (MIPI) Controller                    | 262 |

|           |                        | 7.3.1      | General Description                    | 262 |

|           |                        | 7.3.2      | Features                               | 262 |

|           |                        | 7.3.3      | Programming Model                      | 263 |

|           |                        | 7.3.4      | Initialization/Application Information | 288 |

|           | 7.4                    | subLV      | /DS Controller                         | 289 |

|           |                        | 7.4.1      | General Description                    | 289 |

|           |                        | 7.4.2      | Features                               | 289 |

|           |                        | 7.4.3      | Programming Model                      | 290 |

| Chapter 8 | Video Output Interface |            |                                        | 299 |

|           | 8.1                    | LCD C      | Controller                             | 300 |

|           |                        | 8.1.1      | General Description                    | 300 |

|           |                        | 8.1.2      | Features                               | 300 |

|           |                        | 8.1.3      | Programming Model                      | 301 |

|           | 8.2                    | TVE D      | DAC                                    | 335 |

|           |                        | 8.2.1      | General Description                    | 335 |

|           |                        | 8.2.2      | Features                               | 335 |

|           |                        | 8.2.3      | Programming Model                      | 335 |

| Chapter 9 | Vide                   | o Proces   | ssing                                  | 337 |

|           | 9.1                    | H.264      | Encoder Engine                         | 338 |

|           |                        | 9.1.1      | Video Encoder                          | 338 |

|            | 9.2     | MPEG4                | 4/JPEG Codec Engine            | 340 |

|------------|---------|----------------------|--------------------------------|-----|

|            |         | 9.2.1                | General Description            | 340 |

|            |         | 9.2.2                | Features                       | 341 |

|            | 9.3     | Scalar               |                                | 343 |

|            |         | 9.3.1                | General Description            | 343 |

|            |         | 9.3.2                | Features                       | 344 |

|            |         | 9.3.3                | Memory Map/Register Definition | 345 |

|            | 9.4     | 3D De-               | interlace and De-noise         | 345 |

|            |         | 9.4.1                | General Description            | 345 |

|            |         | 9.4.2                | Features                       | 346 |

|            | 9.5     | 2D Gra               | phics Accelerator Engine       | 346 |

|            |         | 9.5.1                | Features                       | 346 |

|            | 9.6     | Image                | Signal Processor (ISP)         | 347 |

|            |         | 9.6.1                | General Description            | 347 |

|            |         | 9.6.2                | Features                       | 347 |

|            | 9.7     | 3D Noi               | se Reduction                   | 348 |

|            |         | 9.7.1                | Description                    | 348 |

|            |         | 9.7.2                | Features                       | 349 |

| Chapter 10 | Audio   | Interfac             | e                              | 351 |

|            | 10.1    | Audio I              | nput/Output                    | 352 |

|            | 10.2    | I <sup>2</sup> S Cor | ntroller                       | 352 |

|            |         | 10.2.1               | General Description            | 352 |

|            |         | 10.2.2               | Features                       | 353 |

|            |         | 10.2.3               | Programming Model              | 353 |

|            | 10.3    | Audio A              | ADDA and Video DAC Controller  | 362 |

|            |         | 10.3.1               | General Description            | 362 |

|            |         | 10.3.2               | Programming Model              | 362 |

| Chapter 11 | Intelli | gent Vid             | eo Engine                      | 373 |

|            | 11.1    | Introdu              | ction                          | 374 |

|            |         | 11.1.1               | Overview                       | 374 |

|            |         | 11.1.2               | Features                       | 374 |

|            |         | 11.1.3               | Modes of Operation             | 374 |

|            | 11.2    | Memor                | y Map/Register Definition      | 375 |

|            |         | 11.2.1               | Summary of Control Registers   | 375 |

|            |       | 11.2.2   | Register Definitions                   | 376 |

|------------|-------|----------|----------------------------------------|-----|

|            | 11.3  | Functio  | on Description                         | 396 |

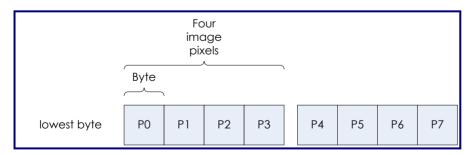

|            |       | 11.3.1   | Source Data Format                     | 396 |

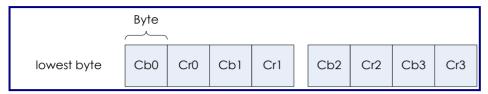

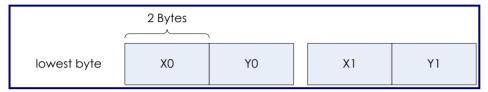

|            |       | 11.3.2   | Destination Data Format                | 397 |

|            |       | 11.3.3   | HSI Conversion                         | 398 |

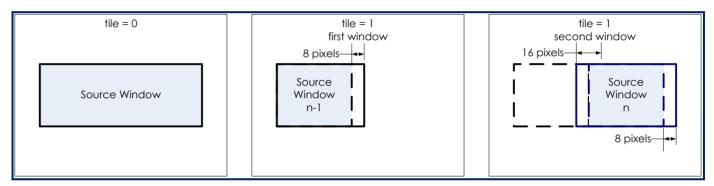

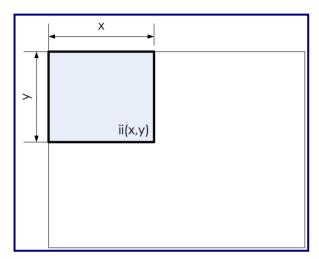

|            |       | 11.3.4   | Integral Image                         | 399 |

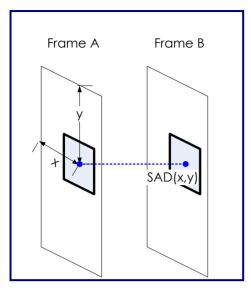

|            |       | 11.3.5   | Sum of Absolute Difference (SAD)       | 399 |

|            |       | 11.3.6   | Raster Operation (ROP)                 | 400 |

|            |       | 11.3.7   | Histogram                              | 401 |

|            |       | 11.3.8   | Convolution                            | 401 |

|            |       | 11.3.9   | Morphology                             | 402 |

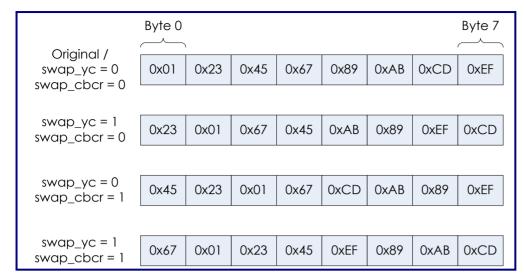

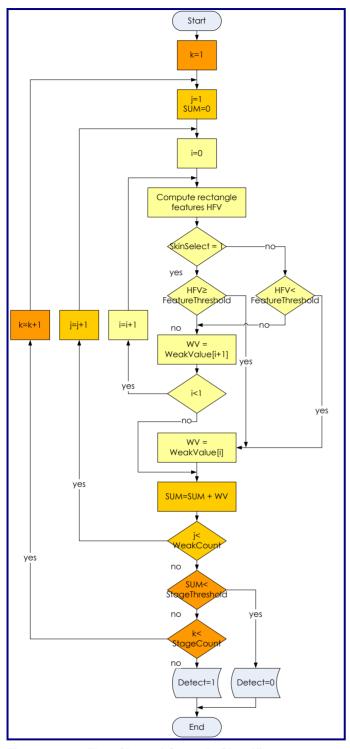

|            |       | 11.3.10  | Cascade Classifier                     | 402 |

| Chapter 12 | High- | Speed I/ | O                                      | 405 |

|            | 12.1  | High-S   | peed I/O Interfaces                    | 406 |

|            | 12.2  | RMII E   | thernet Controller (RMII MAC)          | 406 |

|            |       | 12.2.1   | General Description                    | 406 |

|            |       | 12.2.2   | Features                               | 406 |

|            |       | 12.2.3   | Register Descriptions                  | 407 |

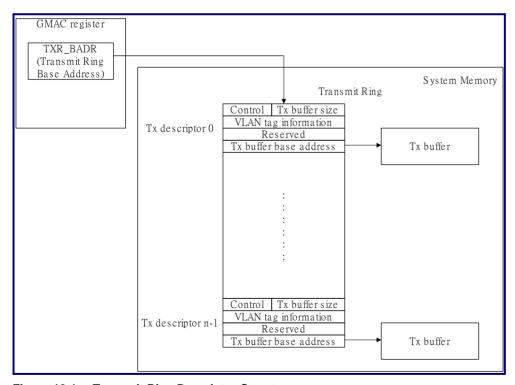

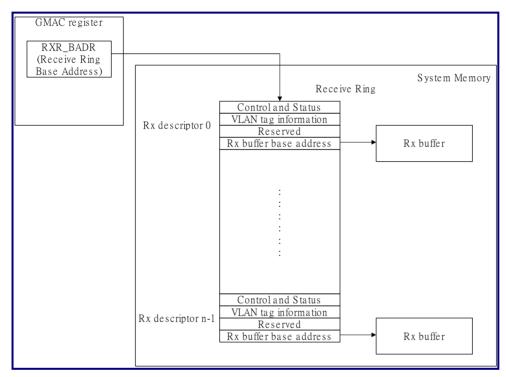

|            |       | 12.2.4   | Functional Description                 | 434 |

|            |       | 12.2.5   | Initialization/Application Information | 447 |

|            |       | 12.2.6   | Ethernet Frame Formats                 | 452 |

|            | 12.3  | Secure   | Digital Controller (SDC)               | 454 |

|            |       | 12.3.1   | General Description                    | 454 |

|            |       | 12.3.2   | Features                               | 454 |

|            |       | 12.3.3   | Memory Map/Register Definition         | 454 |

|            |       | 12.3.4   | Functional Description                 | 499 |

|            |       | 12.3.5   | Initialization                         | 507 |

|            | 12.4  | Univers  | sal Serial Bus (USB)                   | 530 |

|            |       | 12.4.1   | General Description                    | 530 |

|            |       | 12.4.2   | Features                               | 530 |

|            |       | 12.4.3   | Memory Map/Register Definition         | 531 |

| Chapter 13 | Perip | herals   |                                        | 583 |

|            | 13.1  | GPIO C   | Controller                             | 584 |

|            |       | 13.1.1   | General Description                    | 584 |

|            |      | 13.1.2 Features                             | 584 |

|------------|------|---------------------------------------------|-----|

|            |      | 13.1.3 Programming Model                    | 585 |

|            | 13.2 | I <sup>2</sup> C Controller                 | 593 |

|            |      | 13.2.1 General Description                  | 593 |

|            |      | 13.2.2 Features                             | 593 |

|            |      | 13.2.3 Programming Model                    | 594 |

|            | 13.3 | IR Controller                               | 604 |

|            |      | 13.3.1 General Description                  | 604 |

|            |      | 13.3.2 Features                             | 604 |

|            |      | 13.3.3 Programming Model                    | 604 |

|            | 13.4 | UART Controller                             | 609 |

|            |      | 13.4.1 General Description                  | 609 |

|            |      | 13.4.2 Features                             | 609 |

|            |      | 13.4.3 Programming Model                    | 610 |

|            | 13.5 | PWM Controller                              | 624 |

|            |      | 13.5.1 General Description                  | 624 |

|            |      | 13.5.2 Features                             | 624 |

|            |      | 13.5.3 Programming Model                    | 625 |

|            |      | 13.5.4 Function Description                 | 634 |

| Chapter 14 | SAR  | ADC Controller                              | 639 |

|            | 14.1 | General Description                         | 640 |

|            | 14.2 | Features                                    | 640 |

|            | 14.3 | Programming Model                           | 641 |

|            |      | 14.3.1 Summary of ADC Controller Registers  | 641 |

|            |      | 14.3.2 Register Descriptions                | 641 |

| Chapter 15 | DC/A | C Characteristics                           | 647 |

|            | 15.1 | Absolute Maximum Ratings                    | 648 |

|            | 15.2 | Recommended Operating Conditions            | 649 |

|            | 15.3 | Leakage Current and Capacitance             | 649 |

|            | 15.4 | DC Characteristics of 3.3V I/O Buffer Cells | 650 |

|            | 15.5 | AC Timing Characteristics                   | 650 |

|            |      | 15.5.1 I <sup>2</sup> C Timing              | 650 |

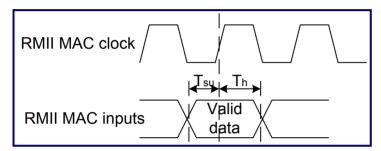

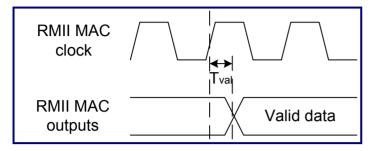

|            |      | 15.5.2 RMII MAC Timing                      | 651 |

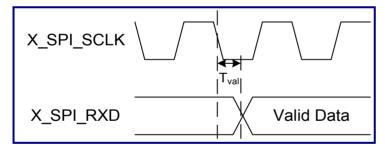

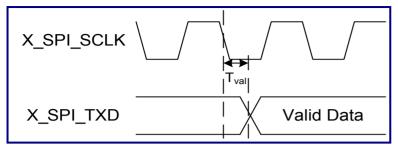

|            |      | 15.5.3 SPI Timing                           | 652 |

|            | 15.5.4 I <sup>2</sup> S Timing             | 653 |

|------------|--------------------------------------------|-----|

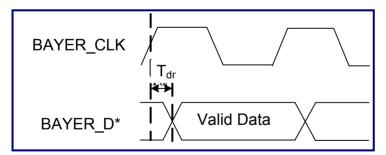

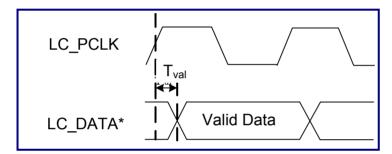

|            | 15.5.5 BT.656/BT.1120 Input Timing         | 655 |

|            | 15.5.6 Parallel Bayer Input Timing         | 655 |

|            | 15.5.7 BT.1120/RGB565/BT.656 Output Timing | 656 |

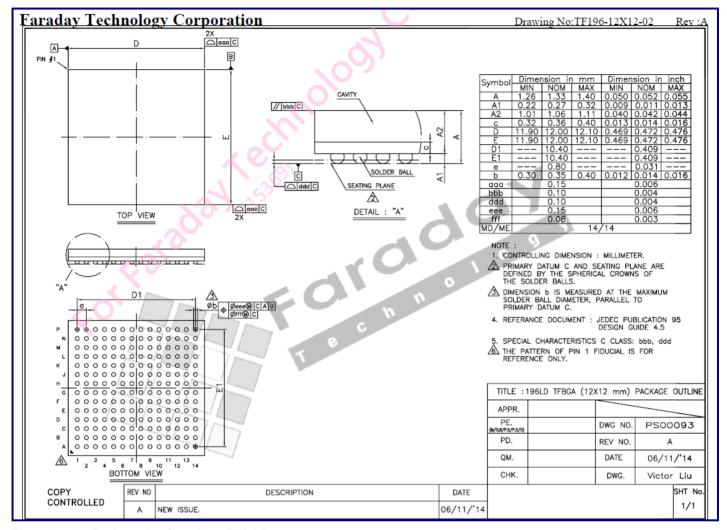

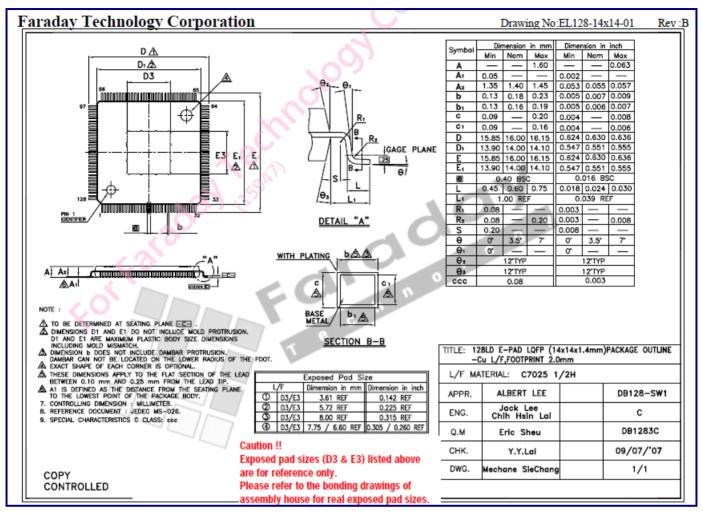

| Chapter 16 | Package Information                        | 657 |

|            | 16.1 Package Dimensions                    | 658 |

## **LIST OF TABLES**

| Table 2-1.  | TFBGA-196 Signal Descriptions                                                     | 20 |

|-------------|-----------------------------------------------------------------------------------|----|

| Table 2-2.  | Pin/Ball Initial State and Default State                                          | 30 |

| Table 2-3.  | Capture in Application Settings                                                   | 34 |

| Table 2-4.  | Jumper Settings                                                                   | 36 |

| Table 4-1.  | Summary of SCU Registers                                                          | 56 |

| Table 4-2.  | ID Number (IDNMBR, Offset = 0x00)                                                 | 58 |

| Table 4-3.  | Jump Setting (Offset = 0x04)                                                      | 59 |

| Table 4-4.  | Power Mode Register (PMR, Offset = 0x0C)                                          | 60 |

| Table 4-5.  | Power Manager Control Register (PMCR, Offset = 0x10)                              | 61 |

| Table 4-6.  | fclk Clock Control Register (Offset = 0x14)                                       | 61 |

| Table 4-7.  | sys_aclk_0 Clock Control Register (Offset = 0x18)                                 | 62 |

| Table 4-8.  | sys_hclk_0 Clock Control Register (Offset = 0x1C)                                 | 62 |

| Table 4-9.  | Power Manager Status Register (Offset = 0x20)                                     | 63 |

| Table 4-10. | sys_pclk_0 Clock Control Register (Offset = 0x24)                                 | 63 |

| Table 4-11. | IP Main Clock Control Setting Register (Offset = 0x28)                            | 64 |

| Table 4-12. | PLL1, PLL2, and PLL3 Bandwidth Option Register (Offset = 0x2C)                    | 66 |

| Table 4-13. | PLL1 Control Register and cpuxx_mode Setting (Offset = 0x30)                      | 67 |

| Table 4-14. | PLL2/PLL3 Control Register (Offset = 0x34)                                        | 68 |

| Table 4-15. | aclk_2_clk Clock Control Register (Offset = 0x38)                                 | 69 |

| Table 4-16. | Driving Capability and Slew Rate and Hold Time Control Register 0 (Offset = 0x40) | 70 |

| Table 4-17. | Driving Capability and Slew Rate and Hold Time Control Register 1 (Offset = 0x44) | 75 |

| Table 4-18. | Bus Bridge Control Register (Offset = 0x48)                                       | 79 |

| Table 4-19. | Multi-function Port Setting Register 0 (MFPSR0, Offset = 0x50)                    | 79 |

| Table 4-20. | Multi-function Port Setting Register 1 (MFPSR1, Offset = 0x54)                    | 82 |

| Table 4-21. | Multi-function Port Setting Register 2 (MFPSR2, Offset = 0x58)                    | 84 |

| Table 4-22. | Multi-function Port Setting Register 3 (MFPSR3, Offset = 0x5C)                    | 85 |

| Table 4-23. | Multi-function Port Setting Register 4 (MFPSR4, Offset = 0x60)                    | 88 |

| Table 4-24. | Multi-function Port Setting Register 5 (MFPSR5, Offset = 0x64)                    | 89 |

| Table 4-25  | PWM0/1 Pin-mux                                                                    | 90 |

| Table 4-26. | Video-in Interface Pin-mux 0                                                  | 91      |

|-------------|-------------------------------------------------------------------------------|---------|

| Table 4-27. | Video-in Interface Pin-mux 1                                                  | 91      |

| Table 4-28. | Video-in Interface Pin-mux 2                                                  | 92      |

| Table 4-29. | Video-in Interface Pin-mux 3                                                  | 92      |

| Table 4-30. | I <sup>2</sup> C Pin-mux                                                      | 93      |

| Table 4-31. | MEMC Pin-mux                                                                  | 94      |

| Table 4-32. | UART2 Pin-mux                                                                 | 94      |

| Table 4-33. | OTG 1(OTG 1.1) Pin-mux                                                        | 95      |

| Table 4-34. | SSP1 Pin-mux                                                                  | 95      |

| Table 4-35. | RMII MAC Pin-mux                                                              | 95      |

| Table 4-36. | GPIO Pin-mux                                                                  | 97      |

| Table 4-37. | ICE Pin-mux                                                                   | 97      |

| Table 4-38. | UART0 Pin-mux                                                                 | 98      |

| Table 4-39. | SPI x-bit Count Setting Register (Offset = 0x6C)                              | 98      |

| Table 4-40. | SDC/MAC/UART/RTC x-bit Count Setting Register (Offset = 0x70)                 | 99      |

| Table 4-41. | SSP/ADC/ADDA x-bit Count Setting Register (Offset = 0x74)                     | 99      |

| Table 4-42. | EXT/Panel Pixel/LCDC Scalar x-bit Count Setting Register (Offset = 0x78)      | 100     |

| Table 4-43. | System Control Register (Offset = 0x7C)                                       | 100     |

| Table 4-44. | DDR3/DDR2 PHY Power Control Setting Register (Offset = 0x80)                  | 103     |

| Table 4-45. | THDNR Clock Control Register (Offset = 0x88)                                  | 103     |

| Table 4-46. | H264 Encoder Clock Control Register (Offset = 0x8C)                           | 104     |

| Table 4-47. | ISP Clock Control Register (Offset = 0x90)                                    | 104     |

| Table 4-48. | GE Clock Control Register (Offset = 0x94)                                     | 104     |

| Table 4-49. | MCP Main Clock Control Register (Offset = 0x98)                               | 105     |

| Table 4-50. | DI Main Clock Control Register (Offset = 0x9C)                                | 105     |

| Table 4-51. | IP Software Reset Control Register 0 (Offset = 0xA0)                          | 106     |

| Table 4-52. | IP Software Reset Control Register 1 (Offset = 0xA4)                          | 108     |

| Table 4-53. | Software Interrupt Set/Clear Control Register (Offset = 0xA8)                 | 108     |

| Table 4-54. | Hardcore Clock Off Control Register (Offset = 0xAC)                           | 109     |

| Table 4-55. | AXI Module Clock Off Control Register (AXIMCLKOFF, Offset = 0xB0)             | 110     |

| Table 4-56. | AHB Module Clock Off Control Register (AHBMCLKOFF, Offset = 0xB4)             | 111     |

| Table 4-57. | APB Module Clock Off Control Register 0 (APBMCLKOFF0, Offset = 0xB8)          | 113     |

| Table 4-58. | APB Module Clock Off Control Register 1 (APBMCLKOFF1, Offset = 0xBC)          | 115     |

| Table 4-59. | OTG 0 PHY/Controller and OTG 1 Controller Control Register 0 (OTGPHY0, Offset | = 0xC0) |

|             |                                                       | 116 |

|-------------|-------------------------------------------------------|-----|

| Table 4-60. | OTG 0 PHY Control Register 1 (OTGPHY1, Offset = 0xC4) | 119 |

| Table 4-61. | Software Register 0 (Offset = 0xD0)                   | 120 |

| Table 4-62. | Software Register 1 (Offset = 0xD4)                   | 120 |

| Table 4-63. | Software Register 2 (Offset = 0xD8)                   | 121 |

| Table 4-64. | Software Register 3 (Offset = 0xDC)                   | 121 |

| Table 4-65. | Interrupt Routing (For cpun_irq_out_r)                | 122 |

| Table 4-66. | Register Summary of Interrupt Controller              | 125 |

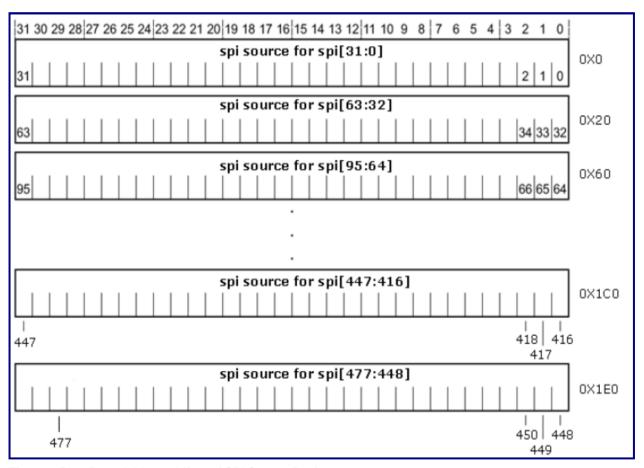

| Table 4-67. | SPI Source Register                                   | 127 |

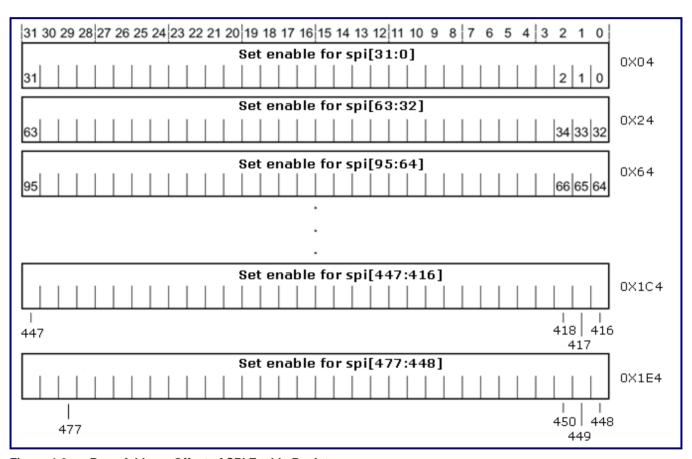

| Table 4-68. | SPI Enable Register                                   | 128 |

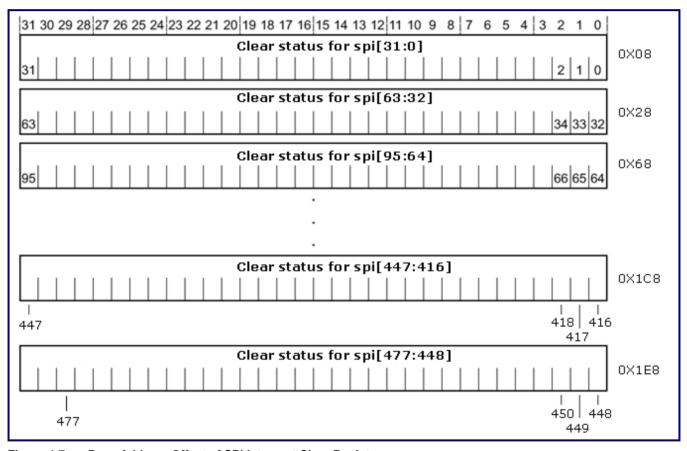

| Table 4-69. | SPI Interrupt Clear Register                          | 129 |

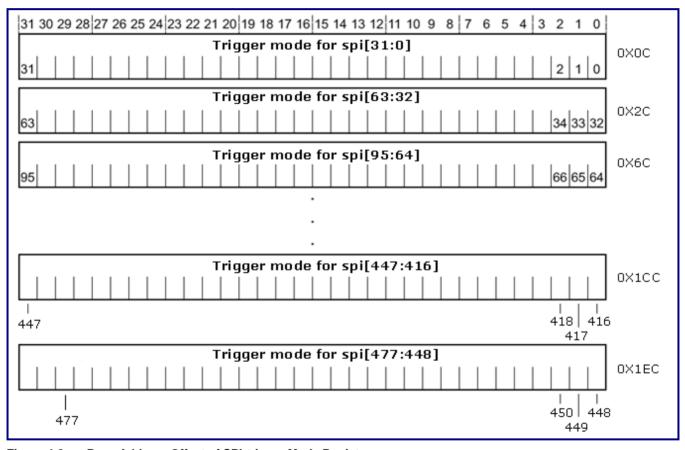

| Table 4-70. | SPI Trigger Mode Register                             | 130 |

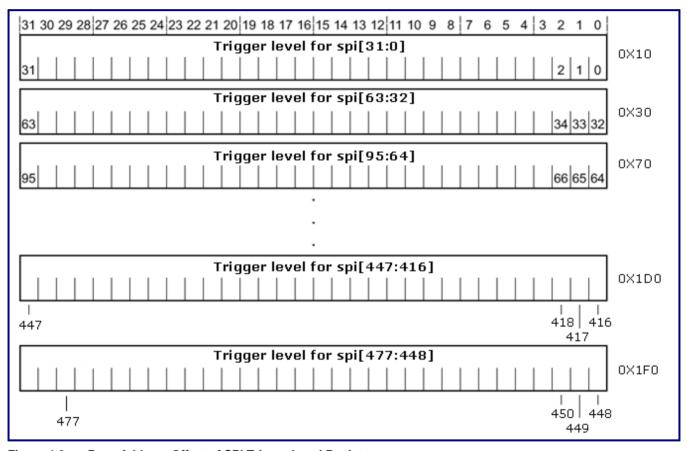

| Table 4-71. | SPI Trigger Level Register                            | 131 |

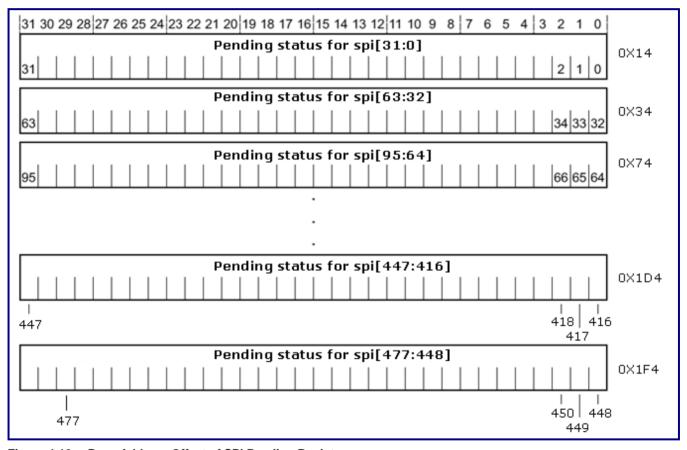

| Table 4-72. | SPI Pending Register                                  | 132 |

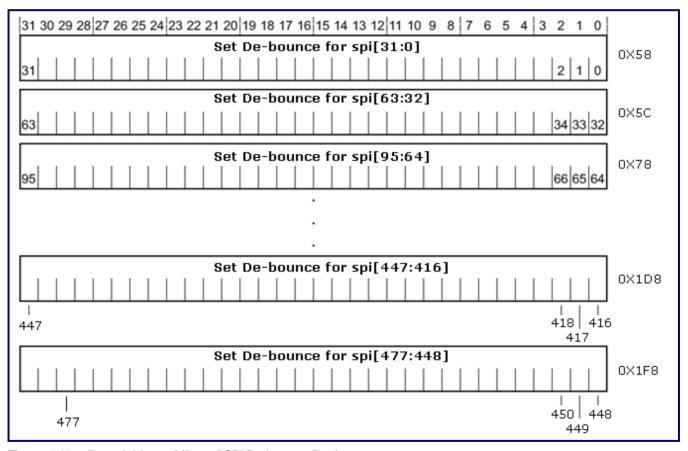

| Table 4-73. | SPI De-bounce Register                                | 133 |

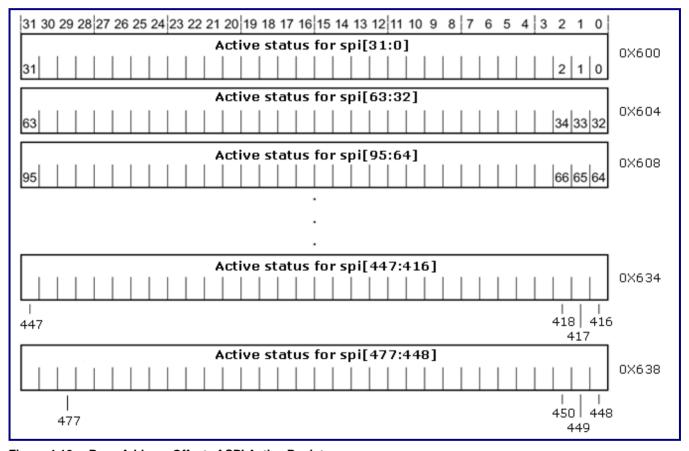

| Table 4-74. | SPI Active Bit Register                               | 134 |

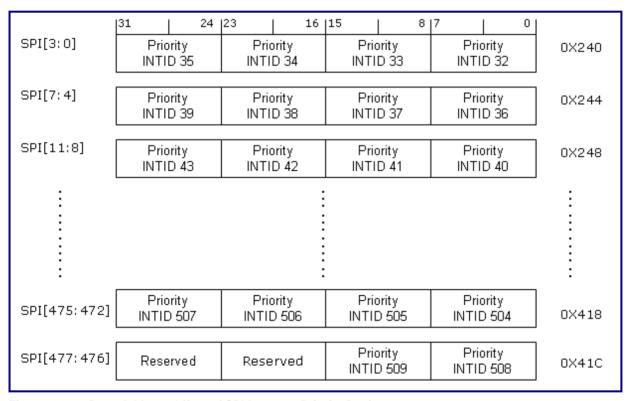

| Table 4-75. | SPI Interrupt Priority Register                       | 135 |

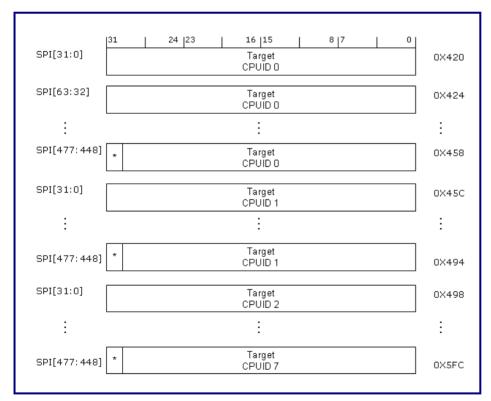

| Table 4-76. | SPI Target Register                                   | 136 |

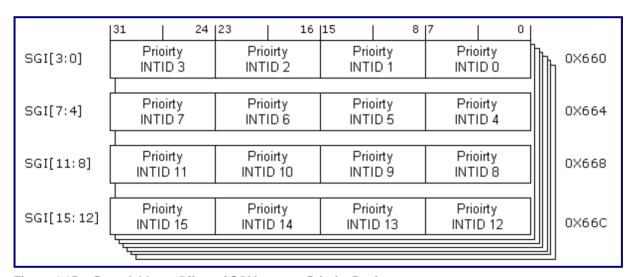

| Table 4-77. | SGI Interrupt Priority Register                       | 137 |

| Table 4-78. | SGI Control Register                                  | 138 |

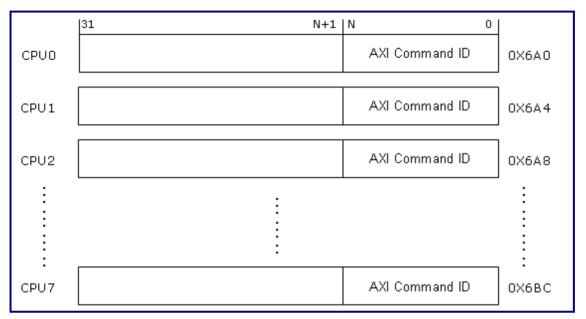

| Table 4-79. | CPU Match Register                                    | 138 |

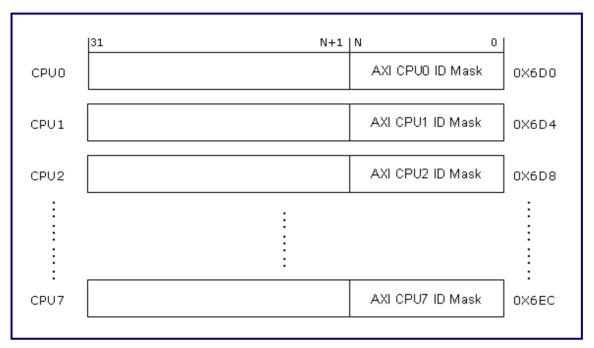

| Table 4-80. | CPU Match Mask Register                               | 139 |

| Table 4-81. | Feature1 Register                                     | 140 |

| Table 4-82. | Revision Register                                     | 141 |

| Table 4-83. | Summary of Timer Registers                            | 145 |

| Table 4-84. | Tm1Counter, Tm2Counter, Tm3Counter Registers          | 146 |

| Table 4-85. | Tm1Load, Tm2Load, Tm3Load Registers                   | 146 |

| Table 4-86. | Tm1Match1, Tm2Match1, Tm3Match1 Registers             | 146 |

| Table 4-87. | Tm1Match2, Tm2Match2, Tm3Match2 Registers             | 147 |

| Table 4-88. | TmCR Register                                         | 147 |

| Table 4-89. | IntrState Register                                    | 149 |

| Table 4-90. | IntrMask Register                                     | 150 |

| Table 4-91. | TmRevision Register                                   | 151 |

| Table 4-92  | Summary of WatchDog Timer Registers                   | 152 |

| Table 4-93.  | WdCounter Register (Offset = 0x00)                                 | 153 |

|--------------|--------------------------------------------------------------------|-----|

| Table 4-94.  | WdLoad Register (Offset = 0x04)                                    | 153 |

| Table 4-95.  | WdRestart Register (Offset = 0x08)                                 | 154 |

| Table 4-96.  | WdCR Register (Offset = 0x0C)                                      | 154 |

| Table 4-97.  | WdStatus Register (Offset = 0x10)                                  | 155 |

| Table 4-98.  | WdClear Register (Offset = 0x14)                                   | 155 |

| Table 4-99.  | WdIntrlen Register (Offset = 0x18)                                 | 155 |

| Table 4-100. | WdRevision Register (Offset = 0x1C)                                | 155 |

| Table 5-1.   | Block Size of Each Mode                                            | 160 |

| Table 5-2.   | Cipher Operation Cycle                                             | 160 |

| Table 5-3.   | Summary of Control Registers                                       | 160 |

| Table 5-4.   | Encryption Control Register (EncryptControl) (Offset = 0x00)       | 162 |

| Table 5-5.   | FIFO Status Register (Offset = 0x08)                               | 163 |

| Table 5-6.   | Parity Error Register (PErrStatus) (Offset = 0x0C)                 | 163 |

| Table 5-7.   | Security Key N Register (KeyN, Offset = 0x10 ~ 0x2C)               | 164 |

| Table 5-8.   | Initial Vector N Registers (IVN, Offset = 0x30 ~ 0x3C)             | 164 |

| Table 5-9.   | DMA Source Address Register (DMASrc, Offset = 0x48)                | 164 |

| Table 5-10.  | DMA Destination Address Register (DMADes, Offset = 0x4C)           | 164 |

| Table 5-11.  | DMA Transfer Size Register (DMATrasSize, Offset = 0x50)            | 165 |

| Table 5-12.  | DMA Control Register (DMACtrl, Offset = 0x54)                      | 165 |

| Table 5-13.  | FIFO Threshold Register (FIFOThold, Offset = 0x58)                 | 166 |

| Table 5-14.  | Interrupt Enable Register (IntrEnable, Offset = 0x5C)              | 166 |

| Table 5-15.  | Interrupt Status Register (IntrSrc, Offset = 0x60)                 | 166 |

| Table 5-16.  | Masked Interrupt Status Register (MaskedIntrStatus, Offset = 0x64) | 167 |

| Table 5-17.  | Interrupt Clear Register (IntrClr, Offset = 0x68)                  | 167 |

| Table 5-18.  | Revision Register (REVISION, Offset = 0x70)                        | 168 |

| Table 5-19.  | Feature Register (FEATURE, Offset = 0x74)                          | 168 |

| Table 5-20.  | Last Initial Vector N Registers (Last_IV N, Offset = 0x80 ~ 0x8C)  | 168 |

| Table 5-21.  | Byte Sequence of Initial Vector                                    | 169 |

| Table 5-22.  | AES-128 Key Stream of Byte Sequence                                | 170 |

| Table 5-23.  | AES-192 Key Stream of Byte Sequence                                | 170 |

| Table 5-24.  | AES-256 Key Stream of Byte Sequence                                | 171 |

| Table 5-25.  | DES Key Stream of Byte Sequence                                    | 171 |

| Table 5-26.  | Triple DES Key Stream of Byte Sequence                             | 171 |

| Table 6-1.  | Summary of DDR Controller Registers                                                  | 177 |

|-------------|--------------------------------------------------------------------------------------|-----|

| Table 6-2.  | Memory Controller Configuration Register (Offset = 0x00)                             | 180 |

| Table 6-3.  | Memory Controller State Control Register (Offset = 0x04)                             | 183 |

| Table 6-4.  | Mode Register Set Value Register of MR and EMR (Offset = 0x08)                       | 186 |

| Table 6-5.  | Mode Register Set Value Register of EMR 2 and EMR 3 (Offset = 0x0C)                  | 187 |

| Table 6-6.  | External Rank0/1 Register (Offset = 0x10)                                            | 187 |

| Table 6-7.  | Timing Parameter 0 Register (Offset = 0x14)                                          | 189 |

| Table 6-8.  | Timing Parameter 1 Register (Offset = 0x18)                                          | 191 |

| Table 6-9.  | Timing Parameter 2 Register (Offset = 0x1C)                                          | 194 |

| Table 6-10. | Command and Data Block Control Register (Offset = 0x20)                              | 196 |

| Table 6-11. | Read Path DLL Delay Tuning Register (Offset = 0x24)                                  | 198 |

| Table 6-12. | COMPBLK Control Register (Offset = 0x28)                                             | 198 |

| Table 6-13. | Automatic Power-down/Self-refresh Control Register (Offset = 0x2C)                   | 199 |

| Table 6-14. | Channel Arbitration Setup Register (Offset = 0x30)                                   | 200 |

| Table 6-15. | Channel Arbiter Grant Count Register - A (Offset = 0x34)                             | 201 |

| Table 6-16. | Write/Read Data Timing Control Register (Offset = 0x3C)                              | 204 |

| Table 6-17. | Command Flush Control Register (Offset = 0x40)                                       | 206 |

| Table 6-18. | Command Flush Status Register (Offset = 0x44)                                        | 206 |

| Table 6-19. | AHB SPLIT Control Register1 (Offset = 0x48)                                          | 207 |

| Table 6-20. | Update Control Register (Offset = 0x4C)                                              | 208 |

| Table 6-21. | User Define Register (Offset = 0x5C)                                                 | 208 |

| Table 6-22. | Write-leveling Control Register (Offset = 0x60) (Only for DDR3 Mode)                 | 209 |

| Table 6-23. | Write-leveling Byte 3 ~ Byte 0 Control Register (Offset = 0x68) (Only for DDR3 Mode) | 210 |

| Table 6-24. | MISC Control Register 1 (Offset = 0x6C) (Only for DDR3 Mode)                         | 211 |

| Table 6-25. | Read-leveling Control Register (Offset = 0x70) (Only for DDR3 Mode)                  | 211 |

| Table 6-26. | msdly Byte Control Register (Offset = 0x74)                                          | 212 |

| Table 6-27. | wrdllsel Control Register (Offset = 0x78)                                            | 213 |

| Table 6-28. | Traffic Monitor Clock Cycle Register (Offset = 0x7C)                                 | 213 |

| Table 6-29. | Command Count Register for Channel 0 (Offset = 0x80)                                 | 213 |

| Table 6-30. | Command Count Register for Channel 1 (Offset = 0x84)                                 | 214 |

| Table 6-31. | Command Count Register for Channel 2 (Offset = 0x88)                                 | 214 |

| Table 6-32. | Command Count Register for Channel 3 (Offset = 0x8C)                                 | 214 |

| Table 6-33. | AHB INCR Read Prefetch Length 1 (Offset = 0xA0)                                      | 215 |

| Table 6-34  | Initialization of Waiting Cycle Count 1 (Offset = 0xA8)                              | 215 |

| Table 6-35. | Initialization of Waiting Cycle Count 2 (Offset = 0xAC)  | 216 |

|-------------|----------------------------------------------------------|-----|

| Table 6-36. | QoS Control Register (Offset = 0xB0)                     | 216 |

| Table 6-37. | QoS Command Control Register A (Offset = 0xB4)           | 217 |

| Table 6-38. | QoS Command Control Register C (Offset = 0xBC)           | 218 |

| Table 6-39. | Channel Arbitration Setup Register B (Offset = 0xC4)     | 219 |

| Table 6-40. | Channel Arbiter Grant Control Register C (Offset = 0xC8) | 220 |

| Table 6-41. | Debug Address (Offset = 0xD0)                            | 222 |

| Table 6-42. | Debug Address Mask (Offset = 0xD4)                       | 222 |

| Table 6-43. | Debug Write Data (Offset = 0xD8)                         | 222 |

| Table 6-44. | Debug Write Data Mask (Offset = 0xDC)                    | 222 |

| Table 6-45. | Debug Master Control (Offset = 0xE0)                     | 223 |

| Table 6-46. | Debug Access Control (Offset = 0xE4)                     | 223 |

| Table 6-47. | Debug Policy Control (Offset = 0xE8)                     | 224 |

| Table 6-48. | Debug Control (Offset = 0xEC)                            | 224 |

| Table 6-49. | Debug Address Status (Offset = 0xF0)                     | 224 |

| Table 6-50. | Debug Write Data Status (Offset = 0xF4)                  | 225 |

| Table 6-51. | Debug Master Status (Offset = 0xF8)                      | 225 |

| Table 6-52. | Debug Access Status (Offset = 0xFC)                      | 225 |

| Table 6-55. | MA Table (AMTSEL = 00) in 8bit DDR3/DDR2 Mode            | 228 |

| Table 6-56. | MA Table (AMTSEL = 00) in 16bit DDR3/DDR2 Mode           | 229 |

| Table 6-57. | MA Table (AMTSEL = 01) in 8bit DDR3/DDR2 Mode            | 230 |

| Table 6-58. | MA Table (AMTSEL = 01) in 16bit DDR3/DDR2 Mode           | 231 |

| Table 6-59. | MA Table (AMTSEL = 10) in 16bit DDR3/DDR2 Mode           | 233 |

| Table 6-60. | Summary of Control Registers                             | 239 |

| Table 6-61. | Command Queue First Word (Address = 0x0000)              | 240 |

| Table 6-62. | Command Queue Second Word (Address = 0x00004)            | 240 |

| Table 6-63. | Command Queue Third Word (Address = 0x0008)              | 242 |

| Table 6-64. | Command Queue Fourth Word (Address = 0x000C)             | 242 |

| Table 6-65. | Control Register (Address = 0x0010)                      | 243 |

| Table 6-66. | AC Timing Register (Address = 0x0014)                    | 244 |

| Table 6-67. | Status Register (Address = 0x0018)                       | 244 |

| Table 6-68. | Interrupt Control Register (Address = 0x0020)            | 245 |

| Table 6-69. | RXFIFO Trigger Level                                     | 245 |

| Table 6-70. | TXFIFO Trigger Level                                     | 245 |

| Table 6-71. | Interrupt Status Register (Address = 0x0024)                        | 246 |

|-------------|---------------------------------------------------------------------|-----|

| Table 6-72. | SPI Read Status Register (Address = 0x0028)                         | 246 |

| Table 6-73. | Revision Register (Address = 0x0050)                                | 246 |

| Table 6-74. | Feature Register (Address = 0x0054)                                 | 246 |

| Table 6-75. | Data Port Register (Address = 0x0100)                               | 247 |

| Table 7-1.  | Mapping of Usual Special-purpose Registers                          | 260 |

| Table 7-2.  | Definition of Register Abbreviation                                 | 263 |

| Table 7-3.  | CSIRX Registers                                                     | 264 |

| Table 7-4.  | Vendor ID Register (VIDR, Offset = 0x00)                            | 265 |

| Table 7-5.  | Device ID Register (DIDR, Offset = 0x01)                            | 265 |

| Table 7-6.  | Control Register (CR, Offset = 0x04)                                | 266 |

| Table 7-7.  | DPI VSync Control Register (VSCR, Offset = 0x05)                    | 267 |

| Table 7-8.  | Extended Control Register (ECR, Offset = 0x06)                      | 268 |

| Table 7-9.  | Timer Count Number Lower Register (TCNLR, Offset = 0x08)            | 268 |

| Table 7-10. | Timer Count Number Higher Register (TCNHR, Offset = 0x09)           | 268 |

| Table 7-11. | HS RX Timeout Value Register (HRTVR, Offset = 0x0A)                 | 269 |

| Table 7-12. | Initialization Timer Lower Register (ITLR, Offset = 0x12)           | 269 |

| Table 7-13. | Initialization Timer Higher Register (ITHR, Offset = 0x13)          | 270 |

| Table 7-14. | DPI VC0 VSync Timing Register (VSTR0, Offset = 0x14)                | 270 |

| Table 7-15. | DPI VC0 HSync Timing Register (HSTR0, Offset = 0x15)                | 270 |

| Table 7-16. | DPI Mapping Control Register (MCR, Offset = 0x1C)                   | 271 |

| Table 7-17. | DPI VSync Timing Extended Register 0 (VSTER0, Offset = 0x1E)        | 271 |

| Table 7-18. | VC0 Horizontal Pixel Number Lower Register (HPNLR0, Offset = 0x20)  | 272 |

| Table 7-19. | VC0 Horizontal Pixel Number Higher Register (HPNHR0, Offset = 0x21) | 272 |

| Table 7-20. | PPI Enable Control Register (PECR, Offset = 0x28)                   | 272 |

| Table 7-21. | Data Lane Mapping Register 0 (DLMR0, Offset = 0x2A)                 | 273 |

| Table 7-22. | CSI Error Report Register 0 (CSIERR0, Offset = 0x30)                | 273 |

| Table 7-23. | CSI Error Report Register 1 (CSIERR1, Offset = 0x31)                | 274 |

| Table 7-24. | Interrupt Status Register (INTSTS, Offset = 0x33)                   | 275 |

| Table 7-25. | Escape Mode and Stop State Register 0 (ESR0, Offset = 0x34)         | 276 |

| Table 7-26. | Escape Mode and Stop State Register 1 (ESR1, Offset = 0x35)         | 276 |

| Table 7-27. | DPI VC0 Status Register (DPISR0, Offset = 0x38)                     | 277 |

| Table 7-28. | Interrupt Enable Register (INTER, Offset = 0x3C)                    | 278 |

| Table 7 20  | CSIRV Footure Register 0 (FERO, Offcot - 0v40)                      | 270 |

| Table 7-30. | VC0 DPCM Register (DPCMR0, Offset = 0x48)                                      | 279 |

|-------------|--------------------------------------------------------------------------------|-----|

| Table 7-31. | CSIRX Revision Register (FRR, Offset = 0x4C)                                   | 280 |

| Table 7-32. | Pixel FIFO Threshold Register (PFTR0, Offset = 0x50)                           | 281 |

| Table 7-33. | CSIRX PHY Control Register 0a (PHYCTRL0a, Offset = 0x60)                       | 281 |

| Table 7-34. | CSIRX PHY Control Register 0b (PHYCTRL0b, Offset = 0x61)                       | 281 |

| Table 7-35. | CSIRX PHY Control Register 0c (PHYCTRL0c, Offset = 0x62)                       | 282 |

| Table 7-36. | CSIRX PHY Control Register 0d (PHYCTRL0d, Offset = 0x63)                       | 282 |

| Table 7-37. | CSIRX PHY Control Register 1a (PHYCTRL1a, Offset = 0x64)                       | 282 |

| Table 7-38. | CSIRX PHY Control Register 1b (PHYCTRL1b, Offset = 0x65)                       | 282 |

| Table 7-39. | CSIRX PHY Control Register 1c (PHYCTRL1c, Offset = 0x66)                       | 282 |

| Table 7-40. | CSIRX PHY Control Register 1d (PHYCTRL1d, Offset = 0x67)                       | 283 |

| Table 7-41. | CSIRX PHY Control Register 2a (PHYCTRL2a, Offset = 0x68)                       | 283 |

| Table 7-42. | RxDataHsSettleCnt                                                              | 283 |

| Table 7-43. | CSIRX PHY Control Register 2b (PHYCTRL2b, Offset = 0x69)                       | 284 |

| Table 7-44. | CSIRX PHY Control Register 2c (PHYCTRL2c, Offset = 0x6A)                       | 284 |

| Table 7-45. | CSIRX PHY Control Register 2d (PHYCTRL2d, Offset = 0x6B)                       | 284 |

| Table 7-46. | CSIRX PHY Control Register 3a (PHYCTRL3a, Offset = 0x6C)                       | 284 |

| Table 7-47. | CSIRX PHY Control Register 3b (PHYCTRL3b, Offset = 0x6D)                       | 285 |

| Table 7-48. | CSIRX PHY Control Register 3c (PHYCTRL3c, Offset = 0x6E)                       | 285 |

| Table 7-49. | CSIRX PHY Control Register 3d (PHYCTRL3d, Offset = 0x6F)                       | 285 |

| Table 7-50. | Frame Control Wrap Register for VC0 (FCWR0, Offset = 0x80)                     | 286 |

| Table 7-51. | Frame Enable Register for VC0 (FER0, Offset = 0x81)                            | 286 |

| Table 7-52. | Frame Number Lower Register for VC0 (FNLR0, Offset = 0x88)                     | 286 |

| Table 7-53. | Frame Number Higher Register for VC0 (FNHR0, Offset = 0x89)                    | 287 |

| Table 7-54. | DPI Built-in Pattern Generator Lower Register for VC0 (BPGLR0, Offset = 0x90)  | 287 |

| Table 7-55. | DPI Built-in Pattern Generator Higher Register for VC0 (BPGHR0, Offset = 0x91) | 287 |

| Table 7-56. | Summary of subLVDS Controller Registers                                        | 290 |

| Table 7-57. | subLVDS_CTRL_Reg (Offset = 0x00)                                               | 291 |

| Table 7-58. | subLVDS_SIZE_Reg (Offset = 0x04)                                               | 293 |

| Table 7-59. | subLVDS_SYNC_Reg (Offset = 0x08)                                               | 293 |

| Table 7-60. | subLVDS_INTR_Reg (Offset = 0x20)                                               | 294 |

| Table 7-61. | subLVDS_VER_Reg (Offset = 0x80)                                                | 294 |

| Table 7-62. | subLVDS_STATUS_Reg0 (Offset = 0x84)                                            | 294 |

| Table 7-63. | subLVDS_STATUS_Reg1 (Offset = 0x88)                                            | 295 |

| Table 7-64. | subLVDS_STATUS_Reg2 (Offset = 0x8C)                         | 295 |

|-------------|-------------------------------------------------------------|-----|

| Table 7-65. | subLVDS_DEBUG_Reg0 (Offset = 0xA0)                          | 295 |

| Table 7-66. | subLVDS_DEBUG_Reg1 (Offset = 0xA4)                          | 295 |

| Table 7-67. | subLVDS_DEBUG_Reg2 (Offset = 0xA8)                          | 296 |

| Table 7-68. | subLVDS_DEBUG_Reg3 (Offset = 0xAC)                          | 296 |

| Table 7-69. | subLVDS_DEBUG_Reg4 (Offset = 0xB0)                          | 296 |

| Table 7-70. | subLVDS_DEBUG_Reg5 (Offset = 0xB4)                          | 296 |

| Table 7-71. | subLVDS_DEBUG_Reg6 (Offset = 0xB8)                          | 297 |

| Table 7-72. | subLVDS_DEBUG_Reg7 (Offset = 0xBC)                          | 297 |

| Table 8-1.  | Summary of LCD Controller Registers                         | 301 |

| Table 8-2.  | LCD Function Enable Parameters (Address = 0x0000)           | 304 |

| Table 8-3.  | LCD Panel Pixel Parameters (Address = 0x0004)               | 306 |

| Table 8-4.  | LCD Interrupt Enable Mask Parameters (Address = 0x0008)     | 309 |

| Table 8-5.  | LCD Interrupt Status Clear Parameters (Address = 0x000C)    | 309 |

| Table 8-6.  | LCD Interrupt Status Parameters (Address = 0x0010)          | 310 |

| Table 8-7.  | Frame Buffer Parameters (Address = 0x0014)                  | 310 |

| Table 8-8.  | Image0 Frame Base Address (Address = 0x0018)                | 311 |

| Table 8-9.  | Image1 Frame Base Address (Address = 0x0024)                | 311 |

| Table 8-10. | PatGen Pattern Bar Distance Parameters (Address = 0x0048)   | 312 |

| Table 8-11. | FIFO Threshold Control Parameters (Address = 0x004C)        | 312 |

| Table 8-12. | Bus Bandwidth Control Parameters (Address = 0x0050)         | 313 |

| Table 8-13. | Revision Registers (Address = 0x0058)                       | 314 |

| Table 8-14. | VBI Base Address (Address = 0x005C)                         | 314 |

| Table 8-15. | FIFO Threshold Control Parameters (Address = 0x0060)        | 314 |

| Table 8-16. | LCD Horizontal Timing Control Parameters (Address = 0x0100) | 315 |

| Table 8-17. | LCD Vertical Timing Control Parameters (Address = 0x0104)   | 316 |

| Table 8-18. | LCD Vertical Back Porch Parameters (Address = 0x0108)       | 316 |

| Table 8-19. | LCD Polarity Control Parameters (Address = 0x010C)          | 317 |

| Table 8-20. | LCD TV Parameter 0 (Address = 0x0204)                       | 318 |

| Table 8-21. | TV Parameter 1 (Address = 0x0204)                           | 320 |

| Table 8-22. | TV Field Polarity Parameter 2 (Address = 0x020C)            | 320 |

| Table 8-23. | TV Vertical Blank Parameter 3 (Address = 0x0210             | 320 |

| Table 8-24. | TV Vertical Blank Parameter 4 (Address = 0x0214)            | 321 |

| Table 8-25  | TV Vertical Active Parameter 5 (Address = 0x0218)           | 321 |

| Table 8-26. | TV Horizontal Blank Parameter 6 (Address = 0x021C)                        | 321 |

|-------------|---------------------------------------------------------------------------|-----|

| Table 8-27. | TV Horizontal Blank Parameter 7 (Address = 0x0220)                        | 321 |

| Table 8-28. | TV Horizontal Active Parameter 8 (Address = 0x0224)                       | 322 |

| Table 8-29. | TV Vertical Blank Parameter 9 (Address = 0x0228)                          | 322 |

| Table 8-30. | TV VBI Parameter 10 (Address = 0x022C)                                    | 322 |

| Table 8-31. | PiP Blending Parameters (Address = 0x0300)                                | 323 |

| Table 8-32. | PiP Sub-Picture1 Position Parameters (Address = 0x0304)                   | 324 |

| Table 8-33. | PiP Sub-picture1 Dimension Parameters (Address = 0x0308)                  | 324 |

| Table 8-34. | PiP Image Priority Parameters (Address = 0x0314)                          | 324 |

| Table 8-35. | PiP/PoP Image Format1 (Address = 0x0318)                                  | 325 |

| Table 8-36. | PiP/PoP Image Format2 (Address = 0x031C)                                  | 327 |

| Table 8-37. | PiP Color Key1 (Address = 0x0320)                                         | 328 |

| Table 8-38. | Palette RAM Write Accessing Port (Address = 0x0A00 ~ 0x0BFC)              | 328 |

| Table 8-39. | Horizontal Input Resolution Register of Scaler Input (Address = 0x1100)   | 329 |

| Table 8-40. | Vertical Input Resolution of Scaler Input (Address = 0x1104)              | 329 |

| Table 8-41. | Horizontal Output Resolution Register of Scaler Output (Address = 0x1108) | 329 |

| Table 8-42. | Vertical Output Resolution Register of Scaler Output (Address = 0x110C)   | 330 |

| Table 8-43. | Miscellaneous Control Register (Address = 0x1110)                         | 330 |

| Table 8-44. | Horizontal High Threshold Register (Address = 0x1114)                     | 331 |

| Table 8-45. | Horizontal Low Threshold Register (Address = 0x1118)                      | 331 |

| Table 8-46. | Vertical High Threshold Register (Address = 0x111C)                       | 331 |

| Table 8-47. | Vertical Low Threshold Register (Address = 0x1120)                        | 332 |

| Table 8-48. | Scaler Resolution Parameters (Address = 0x112C)                           | 332 |

| Table 8-49. | Virtual Screen Control Register (Address = 0x1500)                        | 334 |

| Table 8-50. | Virtual Screen 1 Control Register (Address = 0x1504)                      | 334 |

| Table 10-1. | SSP Control Registers                                                     | 353 |

| Table 10-2. | SSP Control Register 0 (Offset = 0x00)                                    | 354 |

| Table 10-3. | SSP Control Register 1 (Offset = 0x04)                                    | 356 |

| Table 10-4. | SSP Control Register 2 (Offset = 0x08)                                    | 357 |

| Table 10-5. | SSP Status Register (Offset = 0x0C)                                       | 359 |

| Table 10-6. | Interrupt Control Register (Offset = 0x10)                                | 360 |

| Table 10-7. | Interrupt Status Register (Offset = 0x14)                                 | 361 |

| Table 10-8. | Summary of ADDA Controller Registers                                      | 362 |

| Table 10-9. | Audio Codec Control Register 0 (ACR0, Offset = 0x00)                      | 363 |

| Table 10-10. | Audio Codec ADC Control Register 1 (ACR1, Offset = 0x04)                | 365 |

|--------------|-------------------------------------------------------------------------|-----|

| Table 10-11. | Audio Codec Control Register 2 (ACR2, Offset = 0x08)                    | 366 |

| Table 10-12. | Audio Codec Control Register 3 (ACR3, Offset = 0x0C)                    | 368 |

| Table 10-13. | Audio Codec Control Register 4 (ACR4, Offset = 0x10)                    | 370 |

| Table 10-14. | ADC HPFCUT Settings                                                     | 371 |

| Table 10-15. | CVBS DAC Control Register (DACCR, Offset = 0x14)                        | 372 |

| Table 11-1.  | Summary of Control Registers                                            | 375 |

| Table 11-2.  | Control Register (Offset = 0x00)                                        | 376 |

| Table 11-3.  | Parameter Register (Offset = 0x04)                                      | 380 |

| Table 11-4.  | Resolution Register (Offset = 0x08)                                     | 383 |

| Table 11-5.  | Maximum Source Width                                                    | 383 |

| Table 11-6.  | Face Detection Parameter Register (Offset = 0x0C)                       | 383 |

| Table 11-7.  | Read Channel 0 Start Address Register (Offset = 0x10)                   | 384 |

| Table 11-8.  | Read Channel 0 Address Offset Register (Offset = 0x14)                  | 384 |

| Table 11-9.  | Read Channel 1 Start Address Register (Offset = 0x18)                   | 385 |

| Table 11-10. | Read Channel 1 Address Offset Register (Offset = 0x1C)                  | 385 |

| Table 11-11. | Write Channel 0 Start Address Register (Offset = 0x20)                  | 386 |

| Table 11-12. | Write Channel 1 Start Address Register (Offset = 0x24)                  | 386 |

| Table 11-13. | Write Channel 2 Start Address Register (Offset = 0x28)                  | 386 |

| Table 11-14. | Write Channel 3 Start Address Register (Offset = 0x2C)                  | 387 |

| Table 11-15. | Write Channel 4 Start Address Register (Offset = 0x30)                  | 387 |

| Table 11-16. | Write Channel 5 Start Address Register (Offset = 0x34)                  | 388 |

| Table 11-17. | Write Channel 6 Start Address Register (Offset = 0x38)                  | 388 |

| Table 11-18. | Write Channel 7 Start Address Register (Offset = 0x3C)                  | 388 |

| Table 11-19. | Write Channel Address Offset Register (Offset = 0x40)                   | 389 |

| Table 11-20. | Write Channel 2 Start Address Register (Offset = 0x60)                  | 389 |

| Table 11-21. | Read Channel 0 Status Register (Offset = 0x68)                          | 390 |

| Table 11-22. | Read Channel 1 Status Register (Offset = 0x6C)                          | 390 |

| Table 11-23. | Face Detection Status Register r (Offset = 0x70)                        | 390 |

| Table 11-24. | Face Detection Status Register (Offset = 0x74)                          | 391 |

| Table 11-25. | Interrupt Status Register (Offset = 0x78)                               | 391 |

| Table 11-26. | Filter Mask 0 of Kernel Template n (Offset = 0x80 + 0x20 * n)           | 391 |

| Table 11-27. | Filter Mask 1 of Kernel Template n (Offset = 0x80 + 0x20 * n + 0x04)    | 392 |

| Table 11-28  | Filter Mask 2 of Kernel Template n (Offset = $0x80 + 0x20 * n + 0x08$ ) | 392 |

| Table 11-29. | Filter Mask 3 of Kernel Template n (Offset = 0x80 + 0x20 * n + 0x0C)            | . 392 |

|--------------|---------------------------------------------------------------------------------|-------|

| Table 11-30. | Filter Mask 4 of Kernel Template n (Offset = 0x80 + 0x20 * n + 0x10)            | . 393 |

| Table 11-31. | Filter Mask 5 of Kernel Template n (Offset = 0x80 + 0x20 * n + 0x14)            | . 393 |

| Table 11-32. | Filter Mask 6 of Kernel Template n (Offset = 0x80 + 0x20 * n + 0x18)            | . 393 |

| Table 11-33. | Stage Threshold of Haar-Like Features (Offset = 0x0180 ~ 0x037F)                | . 394 |

| Table 11-34. | Weak Value of Haar-Like Features (Offset = 0x2000 ~ 0x3FFF)                     | . 394 |

| Table 11-35. | Feature Threshold of Haar-Like Features (Offset = 0x4000 ~ 0x7FFF)              | . 394 |

| Table 11-36. | Unit Rectangle Information of Haar-Like Features (Offset = 0x8000 ~ 0xBFFF)     | . 395 |

| Table 11-37. | Restrictions on Unit Rectangle                                                  | . 396 |

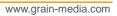

| Table 11-38. | Source Data Format                                                              | . 397 |

| Table 11-39. | Destination Pixel Unit                                                          | . 397 |

| Table 11-40. | Truth Table of Raster Operation                                                 | . 400 |

| Table 11-41. | Example of Raster Operation Code                                                | . 401 |

| Table 12-1.  | Summary of RMII MAC Controller Registers                                        | . 408 |

| Table 12-2.  | Interrupt Status Register (ISR, Offset = 0x0)                                   | . 409 |

| Table 12-3.  | Interrupt Enable Register (IME, Offset = 0x4)                                   | . 410 |

| Table 12-4.  | MAC Most Significant Address Register (MAC_MADR, Offset = 0x8)                  | . 410 |

| Table 12-5.  | MAC Least Significant Address Register (MAC_LADR, Offset = 0xC)                 | . 410 |

| Table 12-6.  | Multicast Address Hash Table 0 Register (MAHT0, Offset = 0x10)                  | . 411 |

| Table 12-7.  | Multicast Address Hash Table 1 Register (MAHT1, Offset = 0x14)                  | . 411 |

| Table 12-8.  | Normal Priority Transmit Poll Demand Register (NPTXPD, Offset = 18h ~ 1Bh)      | . 411 |

| Table 12-9.  | Receive Poll Demand Register (RXPD, Offset = 0x1C)                              | . 411 |

| Table 12-10. | Normal Priority Transmit Ring Base Address Register (NPTXR_BADR, Offset = 0x20) | . 412 |

| Table 12-11. | Receive Ring Base Address Register (RXR_BADR, Offset = 0x24)                    | . 412 |

| Table 12-12. | High Priority Transmit Poll Demand Register (HPTXPD, Offset = 0x28)             | . 412 |

| Table 12-13. | High Priority Transmit Ring Base Address Register (HPTXR_BADR, Offset = 0x2C)   | . 412 |

| Table 12-14. | Interrupt Timer Control Register (ITC, Offset = 0x30)                           | . 413 |

| Table 12-15. | Automatic Polling Timer Control Register (APTC, Offset = 0x34)                  | . 417 |

| Table 12-16. | DMA Burst Length and Arbitration Control Register (DBLAC, Offset = 0x38)        | . 417 |

| Table 12-17. | DMA/FIFO State Register (DMAFIFOS, Offset = 0x3C)                               | . 420 |

| Table 12-18. | Revision Register (REVR, Offset = 0x40)                                         | . 420 |

| Table 12-19. | Feature Register (FEAR, Offset = 0x44)                                          | . 421 |

| Table 12-20. | Transmit Priority Arbitration and FIFO Control Register (TPAFCR, Offset = 0x48) | . 422 |

| Table 12-21. | Receive Buffer Size Register (RBSR, Offset = 0x4C)                              | . 424 |

| Table 12-22. | MAC Control Register (MACCR, Offset = 0x50)                               | 424 |

|--------------|---------------------------------------------------------------------------|-----|

| Table 12-23. | MAC Status Register (MACS, Offset = 0x54)                                 | 426 |

| Table 12-24. | Test Mode Register (TM, Offset = 0x58)                                    | 427 |

| Table 12-25. | PHY Control Register (PHYCR, Offset = 0x60)                               | 427 |

| Table 12-26. | PHY Data Register (PHYDATA) (Offset = 0x64)                               | 428 |

| Table 12-27. | Flow Control Register (FCR, Offset = 0x68)                                | 428 |

| Table 12-28. | Back Pressure Register (BPR, Offset = 0x6C)                               | 429 |

| Table 12-29. | Normal Priority Transmit Ring Pointer Register (NPTXR_PTR, Offset = 0x90) | 430 |

| Table 12-30. | High Priority Transmit Ring Pointer Register (HPTXR_PTR, Offset = 0x94)   | 430 |

| Table 12-31. | Receive Ring Pointer Register (HPTXR_PTR) (Offset = 0x98)                 | 430 |

| Table 12-32. | TPKT_CNT Counter Register (Offset = 0xA0)                                 | 430 |

| Table 12-33. | TXMCOL_CNT and TXSCOL_CNT Counter Register (Offset = 0xA4)                | 431 |

| Table 12-34. | TXECOL_CNT and TXFAIL_CNT Counter Register (Offset = 0xA8)                | 431 |

| Table 12-35. | TXLCOL_CNT and TXUNDERUN_CNT Counter Register (Offset = 0xAC)             | 431 |

| Table 12-36. | RPKT_CNT Counter Register (Offset = 0xB0)                                 | 431 |

| Table 12-37. | BROPKT_CNT Counter Register (Offset = 0xB4)                               | 432 |

| Table 12-38. | MULPKT_CNT Counter Register (Offset = 0xB8)                               | 432 |

| Table 12-39. | RPF_CNT and AEP_CNT Counter Register (Offset = 0xBC)                      | 432 |

| Table 12-40. | RUNT_CNT Counter Register (Offset = 0xC0)                                 | 432 |

| Table 12-41. | CRCER_CNT and FTL_CNT Counter Register (Offset = 0xC4h)                   | 433 |

| Table 12-42. | RCOL_CNT and RLOST_CNT Counter Register (Offset = 0xC8)                   | 433 |

| Table 12-43. | Advance Interrupt Timer Control Register (ITC, Offset = 0xE0)             | 433 |

| Table 12-44. | Frame Structure and Frame Formats                                         | 452 |

| Table 12-45. | Register Types                                                            | 455 |

| Table 12-46. | Summary of SDXC Controller Registers                                      | 455 |

| Table 12-47. | SDMA System Address Register (Offset = 0x00)                              | 457 |

| Table 12-48. | Block Size Register (Offset = 0x04)                                       | 458 |

| Table 12-49. | Block Count Register (Offset = 0x06)                                      | 459 |

| Table 12-50. | Argument 1 Register (Offset = 0x08)                                       | 459 |

| Table 12-51. | Transfer Mode Register (Offset = 0x0C)                                    | 460 |

| Table 12-52. | Transfer Command Settings                                                 | 461 |

| Table 12-53. | Command Register (Offset = 0x0E)                                          | 461 |

| Table 12-54. | Relationship between Parameters and Names of Response Types               | 463 |

| Table 12-55  | Response Registers 0 ~ 3 (Offset = 0x10 ~ 0x1C)                           | 464 |

| Table 12-56. | Response Registers of Each Response Type                        | 464 |

|--------------|-----------------------------------------------------------------|-----|

| Table 12-57. | Buffer Data Port Register (Offset = 0x20)                       | 464 |

| Table 12-58. | Present State Register (Offset = 0x24)                          | 465 |

| Table 12-59. | Host Control 1 Register (Offset = 0x28)                         | 468 |

| Table 12-60. | Power Control Register (Offset = 0x29)                          | 470 |

| Table 12-61. | Block Gap Control Register (Offset = 0x2A)                      | 470 |

| Table 12-62. | Clock Control Register (Offset = 0x2C)                          | 472 |

| Table 12-63. | Timeout Control Register (Offset = 0x2E)                        | 473 |

| Table 12-64. | Software Reset Register (Offset = 0x2F)                         | 473 |

| Table 12-65. | Normal Interrupt Status Register (Offset = 0x30)                | 474 |

| Table 12-66. | Error Interrupt Status Register (Offset = 0x32)                 | 477 |

| Table 12-67. | Normal Interrupt Status Enable Register (Offset = 0x34)         | 478 |

| Table 12-68. | Error Interrupt Status Enable Register (Offset = 0x36)          | 479 |

| Table 12-69. | Normal Interrupt Signal Enable Register (Offset = 0x38)         | 480 |

| Table 12-70. | Error Interrupt Signal Enable Register (Offset = 0x3A)          | 481 |

| Table 12-71. | Auto CMD12 Error Status Register (Offset = 0x3C)                | 481 |

| Table 12-72. | Relationship between CRC Error and Timeout Error for Auto CMD   | 482 |

| Table 12-73. | Host Control 2 Register (Offset = 0x3E)                         | 483 |

| Table 12-74. | Capabilities Register (Offset = 0x40)                           | 484 |

| Table 12-75. | Maximum Current Capabilities Register (Offset = 0x48)           | 488 |

| Table 12-76. | Definitions of Maximum Current Value                            | 488 |

| Table 12-77. | Force Event Register for Auto CMD Error Status (Offset = 0x50)  | 489 |

| Table 12-78. | Force Event Register for Error Interrupt Status (Offset = 0x52) | 489 |

| Table 12-79. | ADMA Error Status Register (Offset = 0x54)                      | 490 |

| Table 12-80. | ADMA System Address Register (Offset = 0x58)                    | 491 |

| Table 12-81. | Preset Value Registers (Offset = 0x60 ~ 0x6F)                   | 491 |

| Table 12-82. | Speed Mode Selection                                            | 492 |

| Table 12-83. | Preset Value Register Based on Speed Mode                       | 492 |

| Table 12-84. | Host Controller Version Register (Offset = 0xFE)                | 493 |

| Table 12-85. | Vendor-defined Register 0 (Offset = 0x100)                      | 493 |

| Table 12-86. | Vendor-defined Register 1 (Offset = 0x104)                      | 494 |

| Table 12-87. | Vendor-defined Register 2 (Offset = 0x108)                      | 495 |

| Table 12-88. | Vendor-defined Register 3 (Offset = 0x10C)                      | 495 |

| Table 12-89. | Vendor-defined Register 4 (Offset = 0x110)                      | 496 |

|              |                                                                 |     |

| Table 12-90.  | Vendor-defined Register 5 (Offset = 0x114)                                     | 496   |

|---------------|--------------------------------------------------------------------------------|-------|

| Table 12-91.  | Vendor-defined Register 6 (Offset = 0x118)                                     | 497   |

| Table 12-92.  | Vendor-defined Register 7 (Offset = 0x11C)                                     | 497   |

| Table 12-93.  | Vendor-defined Register 8 (Offset = 0x120)                                     | 497   |

| Table 12-94.  | Vendor-defined Register 9 (Offset = 0x124)                                     | 498   |

| Table 12-95.  | DMA Handshake Enable Register (Offset = 0x128)                                 | 498   |

| Table 12-96.  | Hardware Attributes Register (Offset = 0x178)                                  | 498   |

| Table 12-97.  | IP Revision Register (Offset = 0x17C)                                          | 499   |

| Table 12-98.  | ADMA Data Length Field                                                         | 503   |

| Table 12-99.  | ADMA States                                                                    | 505   |

| Table 12-100. | Timing Adjustment of SD Interface Output                                       | 506   |

| Table 12-101. | Register Summary                                                               | 532   |

| Table 12-102. | OTG 0(OTG 2.0) Memory-mapped Registers                                         | 533   |

| Table 12-103. | HC Capability Register (HCCAP, Offset = 0x000)                                 | 535   |

| Table 12-104. | HCSPARAMS - HC Structural Parameters (Offset = 0x004)                          | 536   |

| Table 12-105. | HCCPARAMS - HC Capability Parameters (Offset = 0x008)                          | 536   |

| Table 12-106. | USBCMD - HC USB Command Register (Offset = 0x010)                              | 536   |

| Table 12-107. | USBSTS - HC USB Status Register (Offset = 0x014)                               | 539   |

| Table 12-108. | USBINTR - HC USB Interrupt Enable Register (Offset = 0x018)                    | 540   |

| Table 12-109. | FRINDEX - HC Frame Index Register (Offset = 0x01C)                             | 540   |

| Table 12-110. | PERIODICLISTBASE - HC Periodic Frame List Base Address Register (Offset = 0x02 | 4)541 |

| Table 12-111. | ASYNCLISTADDR - HC Current Asynchronous List Address Register (Offset = 0x028) | 541 ( |

| Table 12-112. | PORTSC - HC Port Status and Control Register (Offset = 0x030)                  | 541   |

| Table 12-113. | HC Miscellaneous Register (Offset = 0x040)                                     | 544   |

| Table 12-114. | HC Full-Speed (FS) EOF1 Timing Point Register (Offset = 0x044)                 | 546   |

| Table 12-115. | HC High-Speed (HS) EOF1 Timing Point Register (Offset = 0x048)                 | 547   |

| Table 12-116. | OTG Control Status Register (OTG_CSR, Offset = 0x080)                          | 547   |

| Table 12-117. | OTG Interrupt Status Register (OTG_ISR, Offset = 0x084)                        | 550   |

| Table 12-118. | OTG Interrupt Enable Register (OTG_IER, Offset = 0x088)                        | 551   |

| Table 12-119. | Global HC/OTG/DEV Interrupt Status Register (GLB_ISR, Offset = 0x0C0)          | 552   |

| Table 12-120. | Global Mask of HC/OTG/DEV Interrupt Register (GLB_INT, Offset = 0x0C4)         | 552   |

| Table 12-121. | Device Main Control Register (DEV_CTL, Offset = 0x100)                         | 553   |

| Table 12-122. | Device Address Register (DEV_ADR, Offset = 0x104)                              | 554   |

| Table 12-123  | Device Test Register (DEV/TST_Offset = 0x108)                                  | 555   |

| Table 12-124. | Device SOF Frame Number Register (DEV_SFN, Offset = 0x10C)                                                                  | . 556  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------|--------|

| Table 12-125. | Device SOF Mask Timer Register (DEV_SFN, Offset = 0x110)                                                                    | . 556  |

| Table 12-126. | PHY Test Mode Selector Register (PHY_TST, Offset = 0x114)                                                                   | . 556  |

| Table 12-127. | Device Vendor-Specific I/O Control Register (DEV_VCTL, Offset = 0x118)                                                      | . 557  |

| Table 12-128. | Device CX Configuration Status Register (DEV_CXCFG, Offset = 0x11C)                                                         | . 557  |

| Table 12-129. | Device CX Configuration and FIFO Empty Status Register (DEV_CXCFE, Offset = 0x1                                             | 20)558 |

| Table 12-130. | Device Idle Counter Register (DEV_ICR, Offset = 0x124)                                                                      | . 559  |

| Table 12-131. | Device Mask of Interrupt Group Register (DEV_MIGR, Offset = 0x130)                                                          | . 559  |

| Table 12-132. | Device Mask of Interrupt Source Group 0 Register (DEV_MISG0, Offset = 0x134)                                                | . 560  |

| Table 12-133. | Device Mask of Interrupt Source Group 1 Register (DEV_MISG1, Offset = 0x138)                                                | . 560  |

| Table 12-134. | Device Mask of Interrupt Source Group 2 Register (DEV_MISG2, Offset = 0x13C)                                                | . 562  |

| Table 12-135. | Device Interrupt Group Register (DEV_IGR, Offset = 0x140)                                                                   | . 563  |

| Table 12-136. | Device Interrupt Source Group 0 Register (DEV_ISG0, Offset = 0x144)                                                         | . 564  |

| Table 12-137. | Device Interrupt Source Group 1 Register (DEV_ISG1, Offset = 0x148)                                                         | . 565  |

| Table 12-138. | Device Interrupt Source Group 2 Register (DEV_ISG2, Offset = 0x14C)                                                         | . 567  |

| Table 12-139. | Device Receive Zero-Length Data Packet Register (DEV_RXZ, Offset = 0x150)                                                   | . 569  |

| Table 12-140. | Device Transfer Zero-Length Data Packet Register (DEV_TXZ, Offset = 0x154)                                                  | . 570  |

| Table 12-141. | Device Isochronous Sequential Error/Abort Register (DEV_ISE, Offset = 0x158)                                                | . 570  |

| Table 12-142. | Device IN Endpoint x MaxPacketSize Register (One per Endpoint, $x = 1 \sim 8$ ) (DEV_INN Offset = $0x160 + 4(x - 1)$ )      |        |

| Table 12-143. | Device OUT Endpoint x MaxPacketSize Register (One per Endpoint, $x = 1 \sim 8$ ) (DEV_OUTMPS, Offset = $0x180 + 4(x - 1)$ ) | . 572  |

| Table 12-144. | Device Endpoint 1 ~ 4 Map Register (DEV_EPMAP0, Offset = 0x1A0)                                                             | . 572  |

| Table 12-145. | Device Endpoint 5 ~ 8 Map Register (DEV_EPMAP1, Offset = 0x1A4)                                                             | . 573  |

| Table 12-146. | Device FIFO Map Register (DEV_FMAP, Offset = 0x1A8)                                                                         | . 574  |

| Table 12-147. | Device FIFO Configuration Register (DEV_FCFG, Offset = 0x1AC)                                                               | . 576  |

| Table 12-148. | Device FIFO x Instruction and Byte Count Register (One per FIFO, n = 0 ~ 3) (DEV_FI Offset = 0x1B0 + 4n)                    |        |

| Table 12-149. | Device DMA Target FIFO Number Register (DMA_TFN, Offset = 0x1C0)                                                            | . 578  |